この記事では、一般的な半導体チップ開発プロセスの概要、シリコン前検証とシリコン後検証の違い、SoC/FPGA/ASIC 開発で使用されるツール、半導体設計と製造の新たなトレンド、およびこの分野の VVDN の専門知識について説明します。半導体の設計とエンジニアリングの分野。

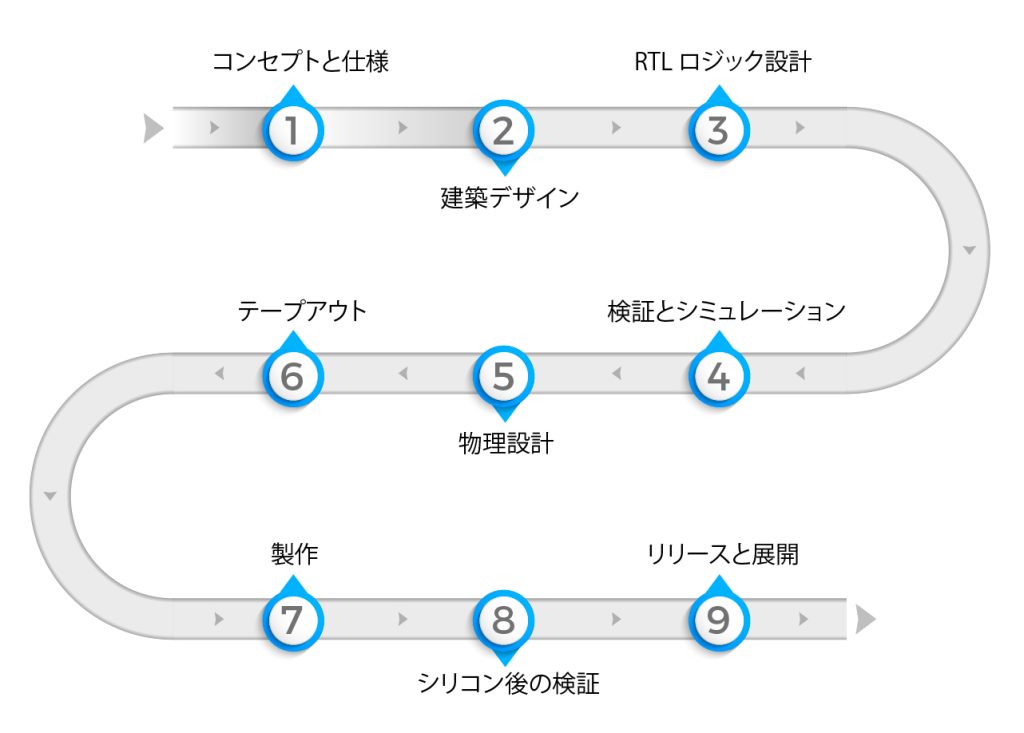

チップの一般的な開発プロセス

半導体または集積回路 (IC) 開発としても知られるチップ開発プロセスには、単純なマイクロコントローラーから高度なプロセッサーまで、幅広いデバイスに電力を供給する電子チップの設計と製造が含まれます。一般的なチップ開発プロセスの概要は次のとおりです。

- コンセプトと仕様:

チップ開発プロセスは、チップの目的、意図される機能、およびターゲット アプリケーションを定義することから始まります。エンジニアと設計者は協力してチップ仕様を作成し、その主要な機能、物理設計、性能要件、消費電力、コスト、電力、その他の重要な特性の概要を示します。

- 建築デザイン:

チップ仕様に基づいて、主要な機能ブロックとその相互接続の概要を示す高レベルのアーキテクチャ設計が開発されます。この段階では、望ましいパフォーマンスを達成するために適切なテクノロジーと方法論を選択することが含まれます。チップ内のインターフェイスとプロトコルもこの段階で定義されます。この段階の結果はその後の段階の基礎として機能し、最適なパフォーマンスを備えた効率的なチップの開発を保証します。

- RTL ロジック設計:

RTL という用語は、レジスタ転送レベルを指します。デジタル設計の目的は、アーキテクチャの概念をチップを表す動作モデルに変換することです。論理設計フェーズでは、チップのアーキテクチャ内の各機能ブロックの詳細な回路図を作成することに重点が置かれます。 Verilog や VHDL などのハードウェア記述言語 (HDL) は、回路のロジックと動作を表すために一般的に使用されます。 RTL デザインは、メモリ ブロック間の論理演算とデータ フローの観点からチップがどのように機能するかを指定します。

- 検証とシミュレーション:

チップを物理的に実装する前に、設計が正しく機能し、仕様を満たしていることを確認するために、広範な検証とシミュレーションが実施されます。これには、潜在的な設計上の欠陥やバグを特定して解決するために、さまざまなテストやシミュレーションを実行することが含まれます。検証段階で見つかった設計上の問題は、修正されるまでデジタル設計チームに送り返されて修正されます。

- 物理設計:

物理設計段階では、チップの論理表現を物理レイアウトに変換します。チップの物理設計は複数のステップに分けることができます (以下に図示)。

- フロアプラン: プロセスはフロアプランから始まり、電子設計自動化 (EDA) ソフトウェアの助けを借りて、トランジスタ、相互接続、およびその他のコンポーネントがチップのシリコン ダイ上に配置されます。

- 配置: 次に、デザイン内のすべての標準セルが配置され、正当な場所が割り当てられる配置です。配置を最適化し、タイミング制約を満たし、信号遅延を最小限に抑えるために、多くの最適化とタイミング主導の配置アルゴリズムが実行されます。

- クロック ツリー合成: クロック ツリー合成 (CTS) は、クロック信号がすべてのシーケンシャル エレメントまたはフロップに均一に分配されるようにするための配置後の段階です。この段階の目的は、設計のタイミング要件を満たす高品質のクロック ネットワークを作成することです。

- ルーティング: ルーティングとは、金属トレースを介してチップ内のさまざまなブロックを相互に接続することです。ルーティングにより、電力整合性と信号整合性 (PI/SI) を最適化しながら、適切な電気接続が保証されます。

- タイミング クロージャとサインオフ: 配線の後、物理設計における重要なステップであるタイミング クロージャとサインオフの段階が始まります。すべてのパスがタイミング要件を満たしていることを確認することで、デザインのパフォーマンスと機能を分析します。

- テープアウト: 物理設計が完全に検証される最終段階であり、グラフィック データ システム (GDS II) 形式の設計データが製造のために半導体ファウンドリに送信されます。

- 製造:

物理設計が完了すると、チップは製造段階に入ります。チップ設計は半導体ファウンドリに送られ、そこでフォトリソグラフィー、エッチング、ドーピングなどのプロセスを経て物理チップが作成されます。

- シリコン後の検証

シリコン検証前の段階で回避されたバグは、シリコン検証後の段階で捕捉されます。ファウンドリから受け取ったチップのプロトタイプは、ラボ設定ですべての機能の正確性を確認するためにリファレンス/評価ボード上でテストされます。検証チェックには、対象となるユースケースの電力とパフォーマンスの遵守、熱変化、電気的ノイズマージン許容度など、機能の正しさ以外にも多くの項目が含まれます。テストは実際のシステム速度で動作するように、実際のチップ上で実行されます。 (GHz の範囲)したがって、これはシリコン検証前の段階と比較して高速です。ポストシリコン検証の全体的な目標は、シリコン/ASIC/SoC/FPGA が認定されており、導入の準備ができていることを確認することです。

- リリースと展開:

チップがすべてのテストおよび品質保証プロセスに合格すると、さまざまな電子デバイスまたはシステムに統合するためにリリースされます。

- リリース後のサポート:

メーカーは継続的なサポートとアップデートも提供し、チップのライフサイクル中に発生する可能性のある問題や改善に対処します。

SoC /FPGA /ASIC開発で使用されるツール:

システムオンチップ (SoC)、フィールドプログラマブルゲートアレイ (FPGA)、および特定用途向け集積回路 (ASIC) の開発には、複雑な集積回路の設計、検証、実装に役立つ幅広いツールが必要です。ハードウェア記述言語 (HDL) エディターと統合開発環境 (IDE) により、効率的なコード作成とシミュレーションが可能になります。論理合成、配置配線、および静的タイミング解析 (STA) ツールは、設計プロセスを最適化し、最適なパフォーマンスを保証します。検証およびデバッグ ツールは、設計段階にある特定のチップの厳密なテストとトラブルシューティングを容易にします。さらに、高位合成 (HLS) およびエミュレーション プラットフォームにより開発が合理化され、電力解析およびフォーマル検証ツールにより効率がさらに向上します。 Cadence、Xilinx/AMD、Intel/Altera、Synopsys、Mentor などの多くの大手企業が、RTL、論理合成、配置配線、静的タイミング解析、物理検証、DFT、シミュレーション、電力解析、およびもっと。これらのツールを使用すると、コンセプトから制作までの過程がシームレスで革新的なエクスペリエンスになります。

半導体開発における新たなトレンド:

半導体またはチップ開発の最新のトレンドは、対象となるアプリケーションで使用できる、より効率的で特殊なプロセッサの必要性によって推進されています。半導体開発のトレンドを牽引するテクノロジーには、5G、モノのインターネット (IoT)、自動運転車、エッジ コンピューティングなどがあります。チップ開発者は、より高速なパフォーマンスのチップを開発するために、異種統合や人工知能などの新しいテクノロジーをチップ開発に採用しています。 7nm、5nm、あるいはそれ以降の半導体テクノロジーも、より優れたパフォーマンスと電力効率を実現しています。これらすべてが集合的に、よりつながりのあるインテリジェントな世界の未来を約束します。

VVDN はチップメーカーの半導体設計とエンジニアリングをどのように支援しますか?

チップの開発プロセスは複雑で、チップの複雑さと関連する製造技術に応じて、数か月から数年かかる場合があります。 VVDN は、世界的なチップ メーカーに幅広い半導体エンジニアリング サービスを提供しています。当社の専門分野は、半導体企業が次世代製品/ソリューションの開発を加速できるよう支援することです。当社の熟練エンジニア チームは、ASIC/SoC/FPGA 開発、RTL 設計、物理設計、シリコン前検証、シリコン後検証、ボードの立ち上げ、リファレンス ハードウェアおよびファームウェアの開発において豊富な経験を持っています。

当社のエンドツーエンドの半導体エンジニアリング能力についてさらに詳しく知りたい場合や、ソリューションの市場投入を加速するためのコラボレーションの機会を検討したい場合は、info@vvdntech.com までお気軽にお問い合わせください。